## Logos系列FPGA器件数据手册

(DS02001, Version2.6) (2021.07.12)

# 深圳市紫光同创电子有限公司 版权所有 侵权必究

## 修订记录

| 日期         | 修订版本 | 描述                                                                                                                                                                       |  |  |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2017.12.19 | V1.0 | 初始发布                                                                                                                                                                     |  |  |

| 2018.12.18 | V1.1 | <ol> <li>统一内核电压和辅助电源电压的符号,分别为VCC和VCCAUX</li> <li>修改表1 Logos系列FPGA用户指南文档,删除封装系列文档,增加《Logos系列产品HMEMC应用实例用户指南》</li> <li>修改章节3.2的上电顺序图</li> </ol>                            |  |  |

| 2019.01.23 | V1.2 | <ol> <li>更新表6-器件绝对极限电压的各参数最小值;</li> <li>更新表格的域和说明</li> </ol>                                                                                                             |  |  |

| 2019.06.03 | V1.3 | 1. 更新产品特性说明; 2. FPGA资源数量表项; 3. 更新封装信息与用户IO数量表项; 4. 删除HSST相关内容; 5. 热插拔直流特性表项; 6. 更新IO直流特性相关表项; 7. 更新交流特性相关表项; 8. 更新典型工作条件下性能参数相关表项 9. 补充缩略语清单                             |  |  |

| 2019.09.25 | V1.4 | 1. 统一电源电压的符号; 2. 更新了fpga产品特性; 3. 更新了资源规模、封装信息以及用户IO数量表项,增加了PGL25G相关信息; 4. 更新了ddr、时钟、配置简要描述; 5. 增加了PGL25G器件工作条件; 6. 增加了PGL25G输入、输出以及输入输出IO电平标准表项; 7. 更新了lvds性能特性、存储接口性能参数 |  |  |

| 2019.12.16 | V1.5 | 1、 修改 <u>表10</u> ,删掉VCCEFUSE、VCCIOCFG两行<br>2、 在DRM描述中 <u>增加了PGL12G不支持ROM的功能</u>                                                                                          |  |  |

| 2020.01.03 | V1.6 | 1、修改表1和表2                                                                                                                                                                |  |  |

| 2020.03.03 | V1.7 | 1、 修改 <u>表7</u> ,增多注意信息<br>2、 修改 <u>表18</u> 、 <u>19</u>                                                                                                                  |  |  |

| 2020.03.09 | V1.8 | 1、 <u>修改1.3.2 DRAM描述</u> 2、 <u>修改1.3.5 硬核和软核的描述</u> 3、修改章节3、4、5标题 4、修改表22、28、30、31、32、33、35 5、修改图2                                                                       |  |  |

| 2020.03.26 | V1.9 | 1、 <u>增加输入AC过冲极限值</u>                                                                                                                                                    |  |  |

DS02001 (v2.6) 第 2 / 48页

| 2020.04.23 | V2.0 | 1、1.1章节增加了 <u>注(2)</u>                                                                                                                                                  |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020.08.13 | V2.1 | 1、增加了PGL50H数据<br>2、 <u>MIPI 性能指标</u>                                                                                                                                    |

| 2020.10.18 | V2.2 | 1、增加PGL50G数据                                                                                                                                                            |

| 2020.12.10 | V2.3 | 1、修改 <u>表47</u> ,HSST_FREFCLK 的指标                                                                                                                                       |

| 2020.03.01 | V2.4 | 1、增加PGL100H数据                                                                                                                                                           |

| 2020.04.07 | V2.5 | 1、更新 <u>表51</u> 数据                                                                                                                                                      |

| 2021.07.12 | V2.6 | 1、增加题注表8         2、更新热插拨特性         3、修改表11,增加VCCEFUSE电压使用范围         4、修改表35,增加从串下降沿的建立时间和保持时间最小值         5、删除表45 HSST_VOUTCMAC指标         6、修改表45 HSST_VRCLKPP最大值为1000mv |

DS02001 (v2.6) 第 **3 / 48**页

## 目 录

| 1Logos系列FPGA概述                 |    |

|--------------------------------|----|

| 1.1Logos系列FPGA产品特性             |    |

| 1.2Logos系列FPGA资源规模与封装信息        | 11 |

| 1.3Logos系列FPGA简要描述             | 11 |

| 1.3.1 CLM                      |    |

| 1.3.2 DRM                      |    |

| 1.3.3 APM                      |    |

| 1.3.4 Input/Output             |    |

| 1.3.5 Memory Controller System |    |

| 1.3.6 ADC                      |    |

| 1.3.7 时钟资源                     |    |

| 1.3.8 配置                       |    |

| 1.4Logos系列FPGA订货信息             |    |

| 2工作条件                          |    |

| 2.1器件绝对极限电压                    |    |

| 2.2输入AC过冲极限值                   |    |

| 2.3器件推荐工作条件                    |    |

| 2.4ESD (HBM, CDM), Latch Up指标  | 20 |

| 3直流特性                          |    |

| 3.1 Hot-Socketing直流特性          | 21 |

| 3.210输入输出直流特性                  | 22 |

| 4交流特性                          | 26 |

| 4.110交流特性参数                    | 26 |

| 4.2CLM交流特性参数                   |    |

| 4.3DRM交流特性参数                   |    |

| 4.4APM交流特性参数                   |    |

| 4.5PLL交流特性参数                   |    |

| 4.6DQS交流特性参数                   |    |

| 4.7全局时钟网络交流特性参数                |    |

| 4.8区域时钟网络交流特性参数                |    |

| 4.910时钟网络交流特性参数                |    |

| 4.10 配置和编程交流特性参数               |    |

| 4.10                           |    |

| 1 0                            |    |

| 4.10.2 各下载模式交流特性               |    |

| 5性能参数                          |    |

| 5.1LVDS性能参数                    |    |

| 5.2 MIPI性能参数                   |    |

| 5.3 存储接口性能参数                   |    |

| 5.4DRM性能参数                     |    |

| 5.5APM性能参数                     |    |

| 6ADC特性参数                       |    |

| 7器件静态电流                        |    |

| 8高速串行收发器(HSSTLP)特性             | 41 |

|                                |    |

| 8.1 HS | STLP硬核绝对极限电压        | 41 |

|--------|---------------------|----|

| 8.2 HS | STLP硬核推荐工作条件        | 42 |

| 8.3 HS | STLP硬核DC直流特性参数      | 43 |

| 8.4高速  | 速串行收发器HSSTLP的AC交流特性 | 43 |

|        |                     |    |

|        | ~<br>作规程及注意事项       |    |

| 10     | 运输与储存               | 47 |

| 11     | 开箱与检查               | 47 |

|        | 质量保障与售后服务           |    |

|        | 联系我们                |    |

|        |                     |    |

## 表目录

| 表  | 1        | LOGOS FPGA资源数量                          | 11 |

|----|----------|-----------------------------------------|----|

|    |          | LOGOS FPGA封装信息与用户IO数量                   |    |

|    |          | Logos系列产品时钟资源                           |    |

|    |          | 配置模式                                    |    |

|    |          | Logos系列FPGA用户指南文档                       |    |

|    |          | 产品质量等级说明                                |    |

|    |          | 器件最大绝对电压值                               |    |

| 表表 |          | 10输入AC过冲电压极限值                           |    |

|    |          | PGL12G、PGL22G推荐工作条件                     |    |

|    |          | PGL 25G推荐工作条件                           |    |

|    |          | PGL50G、PGL50H、PGL100H推荐工作条件             |    |

|    |          | ESD、LATCH-UP指标                          |    |

|    |          | 热插拔直流特性                                 |    |

|    | 13<br>14 |                                         |    |

|    | 15       |                                         |    |

|    |          | , ,, = , ,, , , , , , , , , , , , , , , |    |

|    |          | 输入IO电平标准的BANK支持说明                       |    |

|    |          | 输出IO电平标准的BANK支持说明                       |    |

|    |          | 双向10电平标准的BANK支持说明                       |    |

|    |          | 差分输入标准的参数要求                             |    |

|    | 20       |                                         |    |

|    |          | IOB的输入输出延时                              |    |

|    |          | IOB三态使能时的输出开关特性                         |    |

|    |          | IOL寄存器交流参数                              |    |

|    |          | 输入DESERIALIZER开关参数                      |    |

|    | 25       | ·····                                   |    |

|    |          | CLM模块交流特性                               |    |

|    |          | DRM模块交流特性                               |    |

|    |          | APM模块交流特性                               |    |

|    |          | PLL交流特性                                 |    |

| 表  | 30       | DQS 交流特性                                | 34 |

|    |          | 全局时钟网络交流特性                              |    |

| 表  | 32       | 区域时钟网络交流特性                              | 35 |

| 表  | 33       | IO时钟网络交流特性                              | 35 |

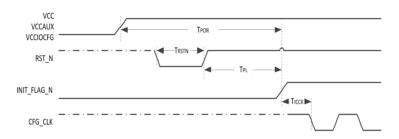

|    |          | POWER-UP TIMING特性参数                     |    |

| 表  | 35       | Logos系列FPGA支持的各下载模式的交流特性                | 36 |

| 表  | 36       | LVDS性能                                  | 38 |

| 表  | 37       | MIPI性能                                  | 38 |

| 表  | 38       | 存储接口性能                                  | 38 |

| 表  | 39       | DRM性能                                   | 39 |

| 表  | 40       | APM性能                                   | 39 |

| 表  | 41       | ADC硬核特性                                 | 40 |

| 表  | 42       | 静态电流                                    | 41 |

| 表  | 43       | HSSTLP绝对极限电压                            | 41 |

|    |          | HSSTLP硬核推荐工作条件                          |    |

|    |          | HSSTLP硬核DC直流特性                          |    |

|    |          | HSSTLP硬核性能参数                            |    |

|    |          | HSSTLP硬核参考时钟开关特性                        |    |

|    |          | HSSTLP硬核PLL/Lock锁定时间特性                  |    |

|    |          | HSSTLP硬核用户时钟开关特性                        |    |

|    |          | HSSTLP硬核TRANSMITTER发送侧开关特性              |    |

|    |          | HSSTLP硬核RECEIVER接收侧开关特性                 |    |

|    |          | PCIE性能参数                                |    |

| 1  | 52       | 1 CID   L     1   2   3                 |    |

## 图目录

| 图 1 Logos系列FPG | A产品型号的编号内容及意义 | 18 |

|----------------|---------------|----|

| 图 2器件Power-up  | ,TIMING特性     | 35 |

缩略语清单: 对本文所用缩略语进行说明,要求提供每个缩略语的英文全名和中文解释

| Abbreviations 缩略语 | Full Spelling 英文全拼          | Chinese Explanation 中文解释 |  |

|-------------------|-----------------------------|--------------------------|--|

| CLM               | Configurable Logic Module   | 可配置逻辑模块                  |  |

| DRM               | Dedicated RAM Module        | 专用RAM存储模块                |  |

| APM               | Arithmetic Process Module   | 算术处理单元                   |  |

| HMEMC             | Hard Memory Controller      | 硬核存储控制器,包含DDRC和DDR PHY   |  |

| DDRC              | Double Data Rate Controller | 内存控制器                    |  |

| DDR               | Double Data Rate            | 双倍速率同步动态随机存储器            |  |

| ADC               | Analog to Digital Converter | 模数转换器                    |  |

| PLL               | Phase Locked Loop           | 锁相环                      |  |

|                   | Hot-Socketing               | 热插拔                      |  |

| ESD               | Electro Static Discharge    | 静电释放                     |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

|                   |                             |                          |  |

DS02001 (v2.6) 第 **8 / 48**页

本文主要包括深圳市紫光同创电子有限公司(以下简称紫光同创)Logos系列 FPGA 器件的特性概要描述、产品型号与资源规模列表、交流、直流特性等内容,用户可以通过本文了解Logos系列FPGA器件特性,方便进行器件选型。

## 1 Logos系列FPGA概述

Logos系列可编程逻辑器件是深圳市紫光同创电子有限公司推出的全新低功耗、低成本FPGA产品,它采用了完全自主产权的体系结构和主流的40nm工艺。Logos系列FPGA包含创新的可配置逻辑模块(CLM)、专用的18Kb存储单元(DRM)、算术处理单元(APM)、多功能高性能IO以及丰富的片上时钟资源等模块,并集成了存储控制器(HMEMC)、模数转换模块(ADC)等硬核资源,支持多种配置模式,同时提供位流加密、器件ID(UID)等功能以保护用户的设计安全。基于以上特点,Logos系列FPGA能够广泛适用于视频、工业控制、汽车电子和消费电子等多个应用领域。

## 1.1 Logos系列FPGA产品特性

- ▶ 低成本、低功耗

- 低功耗、成熟的 40nm CMOS 工艺

- 低至 1.1V 的内核电压

#### ▶ 支持多种标准的IO

- 多达 308 个用户 IO, 支持 1.2V、1.5V、

1.8V、2.5V、3.3V IO 标准

- 支持 HSTL、SSTL 存储接口标准

- 支持 MIPI D-PHY 接口标准

- 支持 LVDS 、 MINI-LVDS 、

SUB-LVDS、SLVS (MIPI 二线电平标准)、TMDS (应用于 HDMI、DVI接口)等差分标准

- 可编程的 IO BUFFER, 高性能的 IO LOGIC

#### ▶ 灵活的可编程逻辑模块CLM

- LUT5 逻辑结构

- 每个 CLM 包含 4 个多功能 LUT5、6

#### 个寄存器

- 支持快速算术进位逻辑

- 支持分布式 RAM 模式

- 支持级联链

#### ▶ 支持多种读写模式的DRM

- 单个 DRM 提供 18Kb 存储空间,可

配置为 2 个独立的 9Kb 存储块

- 支持多种工作模式,包括单口(SP)

RAM、双口(DP)RAM、简单双口(SDP)RAM、ROM以及FIFO模式

- 双口 RAM 和简单双口 RAM 支持双端口混合数据位宽

- 支持 Normal-Write, Transparent-Write

以及 Read-before-Write<sup>(1)</sup>写模式

- 支持 Byte-Write 功能

DS02001 (v2.6) 第 **9 / 48**页

#### ▶ 高效的算术处理单元APM

- 每个 APM 支持 1 个 18\*18 运算或 2

个 9\*9 运算

- 支持输入、输出寄存器

- 支持 48bit 累加器

- 支持 "Signed"以及"Unsigned"数 据运算

#### ▶ 集成存储控制器硬核HMEMC

- 支持 DDR2、DDR3、LPDDR

- 单个 HMEMC 支持 x8、x16 数据位宽

- 支持标准的 AXI4 总线协议

- 支持 DDR3 write leveling 和 DQS gate training

- DDR3 最高速率达 800Mbps

#### ▶ 集成ADC硬核

- 10bit 分辨率、1MSPS(独立 ADC 工作)采样率

- 多达 12 个输入通道

- 集成温度传感器

#### > 丰富的时钟资源

- 支持3类时钟网络,可灵活配置

- 基于区域的全局时钟网络

- 每个区域有4个区域时钟,支持垂直 级联

- 高速 IO 时钟, 支持 IO 时钟分频

- 可选的数据地址锁存、输出寄存器

- 集成多个 PLL,每个 PLL 支持多达 5 个时钟输出

## ▶ 灵活的配置方式

- 支持多种编程模式

- JTAG 模式符合 IEEE 1149 和 IEEE 1532 标准

- Master SPI 可选择最高 8bit 数据位

宽, 有效提高编程速度

- 支持 BPI x8/x16、Serial slave、Parallel slave 模式

- 支持 AES-256 位流加密<sup>(2)</sup>, 支持 64bit

UID 保护

- 支持 SEU 检错纠错

- 支持多版本位流回退功能

- 支持看门狗超时检测

- 支持编程下载

- 支持在线调试

注(1): 不支持两个端口同时配置为 Read-before-Write 模式

注(2): PGL25G 不支持 AES-256 位流加密

DS02001 (v2.6) 第 **10 / 48**页

#### 1.2 Logos系列FPGA资源规模与封装信息

Logos系列FPGA资源规模与封装信息如表 1和表 2所示。

CLM<sup>1, 2</sup> MAX 18Kb **HME** APM **PLL ADC USER HSST** SD 等效 Distributed **DRM** 器件 MC LUT5 FF (个) (个) (个) Ю **RAM** LANE RAM LUT4 (个) (个) (个) (个) (个) (bits) (个) PGL12G PGL22G PGL22GS<sup>3</sup> PGL25G PGL50G PGL50H PGL100H

表 1 Logos FPGA资源数量

- 注1:每个CLM包含4个多功能LUT5和6个寄存器;每个多功能LUT5等效为1.2个LUT4

- 注2: 芯片中的CLM包括CLMA和CLMS,仅CLMS可配置为Distributed RAM。

- 注3: PGL22GS-176包含最大IO数量为140, 其中包括68对差分对和4个单端IO; MAX USER IO 140个表示芯片外

部可用IO管脚,芯片内部额外包含与SDRAM连接的管脚。

| 农 2 20800 11 4031% [[18-5/11/10 ]] |         |         |         |               |         |         |         |

|------------------------------------|---------|---------|---------|---------------|---------|---------|---------|

| 封装                                 | FBG256  | FBG484  | FBG900  | <b>MBG484</b> | MBG324  | LPG176  | LPG144  |

| 尺寸 (mm)                            | 17×17   | 23×23   | 31×31   | 19×19         | 15×15   | 22x22   | 22x22   |

| Pitch (mm)                         | 1.0     | 1.0     | 1.0     | 0.8           | 0.8     | 0.4     | 0.5     |

| 器件                                 | User IO | User IO | User IO | User IO       | User IO | User IO | User IO |

| PGL12G                             | 160     | -       | -       | -             | -       | -       | 103     |

| PGL22G                             | 186     | -       | -       | -             | 240     | -       | -       |

| PGL22GS                            | -       | -       | -       | -             | -       | 140     | -       |

| PGL25G                             | 186     | 308     | -       | -             | 226     | -       | -       |

| PGL50G                             | -       | 332     | -       | 341           | 218     | -       | -       |

| PGL50H                             | -       | 296     | -       | 304           | 190     | -       | -       |

| PGL100H                            | -       | -       | 498     | -             | -       | -       | -       |

表 2 Logos FPGA封装信息与用户10数量

## 1.3 Logos系列FPGA简要描述

#### 1.3.1 CLM

CLM(Configurable Logic Module,可配置逻辑模块)是Logos系列产品的基本逻辑单元,它主要由多功能LUT5,寄存器以及扩展功能选择器等组成。CLM在Logos系列产品中按列分布,有CLMA和CLMS 两种形态。CLMA和CLMS均支持逻辑功能,算术功能以及寄存器功能,仅有CLMS支持分布式RAM功能。CLM与CLM之间,CLM与其它片内资源之间通过信号互连模块联结。

每个CLMA包含4个LUT5、6个寄存器、多个扩展功能选择器、以及4条独立的级联链等。

DS02001 (v2.6) 第 **11 / 48**页

CLMS是CLMA的扩展,它在支持CLMA所有功能的基础上增加了对分布式RAM的支持。CLMS可配置为单口 RAM或者简单双口RAM。

#### 1.3.2 DRM

单个DRM有18K bits存储单元,可以独立配置2个9K或1个18K,其支持多种工作模式,包括双口RAM,简单双口 RAM,单口RAM或ROM模式,以及FIFO模式。DRM支持可配置的数据位宽,并在DP RAM和SDP RAM模式下支持双端口混合数据位宽。对于PGL12G,不支持ROM。详细的DRM使用可参考《Logos系列FPGA专用RAM模块(DRM)用户指南》。

#### 1.3.3 APM

每个APM由I/O Unit, Preadder, Mult和Postadder功能单元组成,支持每一级寄存器流水。每一个APM可实现1个18\*18乘法器或两个9\*9乘法器,支持预加功能;可实现1个48bit累加器或2个24bit累加器。Logos FPGA的APM支持级联,可实现滤波器以及高位宽乘法器应用。

#### 1.3.4 Input/Output

#### **IOB**

Logos FPGA的IO按照Bank分布,每个Bank由独立的IO电源供电。IO灵活可配置,支持 1.2V~3.3V电源电压以及不同的单端和差分接口标准,以适应不同的应用场景。所有的用户IO 都是双向的,内含IBUF、OBUF以及三态控制TBUF。Logos FPGA的IOB功能强大,可灵活配置接口标准、输出驱动、Slew Rate、输入迟滞等。详细的IO特性及使用方法可参考《Logos系列FPGA输入输出接口(IO)用户指南》。

#### **IOL**

IOL模块位于IOB和core之间,对要输入和输出FPGA Core的信号进行管理。

IOL支持各种高速接口,除了支持数据直接输入输出、IO寄存器输入输出模式外,还支持以下功能:

- ▶ ISERDES: 针对高速接口,支持1:2: 1:4: 1:7: 1:8的输入串并转换器。

- ▶ OSERDES: 针对高速接口,支持2:1; 4:1; 7:1; 8:1的输出并串转换器。

- ▶ 内置IO延迟功能,可以动/静态调整输入/出延迟。

- ▶ 内置输入FIFO,主要用于完成从外部非连续DQS(针对DDR memory interface)到内部 连续时钟的时钟域转换和一些特殊的Generic DDR应用中采样时钟和内部时钟的相差

DS02001 (v2.6) 第 **12 / 48**页

补偿。

#### 1.3.5 Memory Controller System

PGL DDR Memory Controller System 为用户提供一套完整的DDR memory控制器解决方案,配置方式比较灵活。

PGL22G集成了HMEMC,有如下特点:

- ➤ 支持LPDDR, DDR2, DDR3

- ➤ 支持x8、x16 Memory Device

- ➤ 支持标准的AXI4总线协议(burst type不支持fixed)

- ▶ 一共三个AXI4 Host Port, 1个128bit,两个64bit

- ➤ 支持 AXI4 Read Reordering

- ➤ 支持 BANK Management

- > 支持Low Power Mode, Self refresh, Power down, Deep Power Down

- ➤ 支持Bypass DDRC、支持Bypass HMEMC

- ➤ 支持DDR3 Write Leveling 和DQS Gate Training

- ➤ DDR3最快速率达800 Mbps

PGL12G、PGL25G、PGL50G、PGL50H、PGL100H只能采用软核实现DDR memory的控制,有如下特点:

- ➤ 支持DDR3

- ➤ 支持x8、x16 Memory Device

- ▶ 最大位宽支持16 bit

- ▶ 支持裁剪的AXI4总线协议

- ➤ 一个AXI4 128bit Host Port

- > 支持Self refresh, Power down

- ▶ 支持Bypass DDRC

- ➤ 支持DDR3 Write Leveling 和DQS Gate Training

- ➤ DDR3最快速率达800 Mbps

#### 1.3.6 ADC

每个ADC分辨率为10bit、采样率为1MSPS,有12个Channels,其中10个Analog Input与GPIO

DS02001 (v2.6) 第 **13 / 48**页

复用,另外2个采用专用模拟输入引脚。12个Channels的扫描方式完全由FPGA灵活控制,用户可以通过User Logic决定最终由几个Channels分享1MSPS的ADC采样率。

ADC提供对片上电压及温度的监测功能。可对VCC、VCCAUX、VDDM(内部LDO输出电压)进行检测:详细特性参数见表 40。

#### 1.3.7 时钟资源

Logos系列产品被划分为不同数量的区域,提供了丰富的片上时钟资源,包含PLL以及三类时钟网络:全局时钟、区域时钟、I/O时钟。其中IO时钟相比其他时钟具有频率高、时钟偏移小以及延时时间小的特点。时钟资源详见表 3。

| 表 o Logosが列 Hiri J M 及M |        |        |        |                  |              |  |  |  |

|-------------------------|--------|--------|--------|------------------|--------------|--|--|--|

| 特性                      | PGL12G | PGL22G | PGL25G | PGL50H<br>PGL50G | PGL100H      |  |  |  |

| 区域数量                    | 4      | 6      | 4      | 6                | 10           |  |  |  |

| 全局时钟数                   | 20     | 20     | 20     | 30               | 30           |  |  |  |

| 每个区域                    | 16     | 12     | 16     | 16               | 16           |  |  |  |

| 支持全局时钟数                 |        |        |        |                  |              |  |  |  |

| 每个区域                    | 4      | 4      | 4      | 4                | 4            |  |  |  |

| 支持局域时钟数                 |        |        |        |                  |              |  |  |  |

| IO BANK数                | 4      | 6      | 4      | 4                | 6            |  |  |  |

| 每个IO BANK               | 2      | 2      | 4      | BANK0/2 : 4      | BANK0/2 : 4  |  |  |  |

| 支持IO时钟数                 |        |        |        | BANK1/3 : 6      | BANK1/3 : 10 |  |  |  |

| 总IO时钟数                  | 8      | 12     | 16     | 20               | 28           |  |  |  |

| PLL数量                   | 4      | 6      | 4      | 5                | 8            |  |  |  |

表 3 Logos系列产品时钟资源

Logos FPGA内嵌多个PLL,每个PLL多达5个时钟输出,支持频率综合、相位调整、动态配置、支持源同步、零延时缓冲等模式,另外,PLL支持Power Down,如果在某一段时间内不使用PLL,用户可以关闭PLL以达到降低功耗的目的。

为了提高时钟的性能,Logos FPGA还提供了CLK相关的特殊IO,包括四类:时钟输入管脚、PLL参考时钟输入管脚、PLL反馈输入时钟管脚以及PLL时钟输出管脚。和普通IO相比,使用这些时钟输入/输出管脚可以避免普通布线资源带来的干扰,从而得到较好的时钟性能。不作为时钟输入/输出时,这些时钟管脚可作为普通IO使用。关于时钟具体使用详情见《Logos系列FPGA时钟资源(Clock)用户指南》。

#### 1.3.8 配置

配置(configuration)是对FPGA进行编程的过程。Logos FPGA使用SRAM单元存储配置数据,每次上电后都需要重新配置;配置数据可以由芯片主动从外部flash获取,也可通过外部处

DS02001 (v2.6) 第 **14/48**页

理器或控制器将配置数据下载到芯片中。

Logos FPGA支持多种配置模式,包括JTAG模式、SPI Master模式、SPI Slave模式、Parallel Slave模式、Serial Slave模式和主BPI模式。各个器件支持的配置模式如下表 4。

|               |        | PGL     | 12G   | PGI   | .22G         | PGL22GS  | PGL25G      | PGL50H     | PGL    |

|---------------|--------|---------|-------|-------|--------------|----------|-------------|------------|--------|

|               | 数据     |         |       |       |              |          |             | PGL50G     | 100H   |

| 模式            | 位宽     | LPG144  | FBG   | FBG   | MBG          | LPG176   | FBG256      | FBG484     | FBG900 |

|               | 14. An | LI 0144 | 256   | 256   | 324          | LI GI /0 | MBG324      | MBG484     |        |

|               |        |         |       |       |              |          | FBG484      | MBG324     |        |

| JTAG          | 1      | 支持      | 支持    | 支持    | 支持           | 支持       | 支持          | 支持         | 支持     |

|               | 1      | 不支持     | 支持    | 支持    | 支持           | 支持       | 支持          | 支持         | 支持     |

| SPIMaster     | 2      | 不支持     | 支持    | 支持    | 支持           | 支持       | 支持          | 支持         | 支持     |

| STIVIASICI    | 4      | 不支持     | 支持    | 支持    | 支持           | 支持       | 支持          | 支持         | 支持     |

|               | 8      | 不支持     | 支持    | 支持    | 支持           | 支持       | 不支持         | 不支持        | 不支持    |

| SPI Slave     | 1      | 支持      | 支持    | 支持    | 支持           | 不支持      | 不支持         | 不支持        | 不支持    |

|               | 8      | 支持      | 支持    | 支持    | 支持           | 不支持      | 支持          | 支持         | 支持     |

| ParallelSlave | 16     | 支持      | 支持    | 支持    | 支持           | 不支持      | 支持          | 支持         | 支持     |

|               | 32     | 支持      | 支持    | 不支持   | 支持           | 不支持      | 不支持         | 不支持        | 不支持    |

| SerialSlave   | 1      | 支持      | 支持    | 支持    | 支持           | 不支持      | 支持          | 支持         | 支持     |

|               | 8(异    | 不支持     | 不支持   | 不支持   | 支持           | 不支持      | 支持          | 支持         | 支持     |

|               | 步)     | 1.文1)   | 小文的   | 1.文1  | 文1/1         | 小文羽      | 文1/1        | <b>X10</b> | 又的     |

| BPI Master    | 16 (异  | 不支持     | 不支持   | 不支持   | 支持           | 不支持      | 支持          | 支持         | 支持     |

| Di i mastei   | 步)     |         |       |       | <b>V</b> 111 |          | <b>✓</b> 14 | 714        | V11    |

|               | 16 (同  | 不支持     | 不支持   | 不支持   | 支持           | 不支持      | 不支持         | 不支持        | 不支持    |

|               | 步)     | 1 ~,3   | 1 ~13 | 1 ~13 | ~13          | 1 ~13    | 1 ~ 13      | 1 2,13     | 1 ~13  |

表 4 配置模式

Logos FPGA的配置相关功能如下所述:

- ▶ 支持配置数据流压缩,可有效减小 bit 流的大小,节约存储空间和编程时间

- ▶ 支持通过 JTAG 接口、从并行接口进行 SEU 1bit 纠错和 2bit 检错

- ▶ 支持看门狗超时检测功能

- ▶ 在主 BPI/主 SPI 模式下,支持配置位流版本回退功能

为保护用户设计,Logos FPGA还提供UID功能。每一个FPGA器件都有一个与之对应的唯一编号,该编号在器件出厂的时候已经唯一确定。用户可以通过UID接口和JTAG接口读取,并且以自己特有的加密算法处理后将得到的结果并入编程数据流。每一次重载数据流后,FPGA

DS02001 (v2.6) 第 **15 / 48**页

进入用户模式,用户逻辑都会先读取该UID以用户独特的加密算法处理后与之前编程数据流中的结果相比对,若有不同,则FPGA无法正常工作。

DS02001 (v2.6) 第 **16 / 48**页

## Logos系列FPGA参考资料

1.3小节对Logos FPGA各模块以及时钟和配置系统做了简要描述,要了解相应模块的详细信息,请查阅Logos FPGA相关的用户指南文档,见下表 5。

表 5 Logos系列FPGA用户指南文档

| 文档编号                 | 文档名称                                                     | 文档内容                                         |

|----------------------|----------------------------------------------------------|----------------------------------------------|

| UG020001             | 《Logos系列FPGA可配置逻辑模块(CLM)用户指南》                            | Logos系列FPGA可配置逻辑模块功能描述                       |

| UG020002             | 《Logos系列FPGA专用RAM模块(DRM)用户指南》                            | Logos系列FPGA专用RAM模块功能描述                       |

| UG020003             | 《Logos系列FPGA算术处理模块(APM)用户指南》                             | Logos系列FPGA算术处理模块功能描述                        |

| UG020004             | 《Logos系列FPGA时钟资源(Clock)用户指南》                             | Logos系列FPGA时钟资源,包括PLL的功能与用法描                 |

| 0 0020001            | "Dogoodity iii orini yi ya wa Colocie, yiiy iiiiia"      | 述                                            |

| UG020005             | 《Logos系列FPGA配置(configuration)用户指南》                       | Logos系列FPGA配置接口、配置模式、配置过程等的                  |

| 0 0020003            | "Dogoodity 111 Office (comigatation) /11/ 11111/         | 描述                                           |

| UG020006             | 《Logos系列FPGA输入输出接口(IO)用户指南》                              | Logos系列FPGA输入输出接口功能描述                        |

| UG020009             | 《Logos系列FPGA模数转换模块(ADC)用户指南》                             | Logos系列FPGA模数转换器功能描述                         |

| UG020011             | 《Logos系列产品HMEMC应用实例用户指南》                                 | Logos系列FPGA存储控制系统应用实例描述                      |

| UG020013             | 《Logos系列FPGA高速串行收发器(HSST)用户指南》                           | Logos系列FPGA高速串行收发器应用描述                       |

| UG020009<br>UG020011 | 《Logos系列FPGA模数转换模块(ADC)用户指南》<br>《Logos系列产品HMEMC应用实例用户指南》 | Logos系列FPGA模数转换器功能描述 Logos系列FPGA存储控制系统应用实例描述 |

DS02001 (v2.6) 第 **17 / 48**页

## 1.4 Logos系列FPGA订货信息

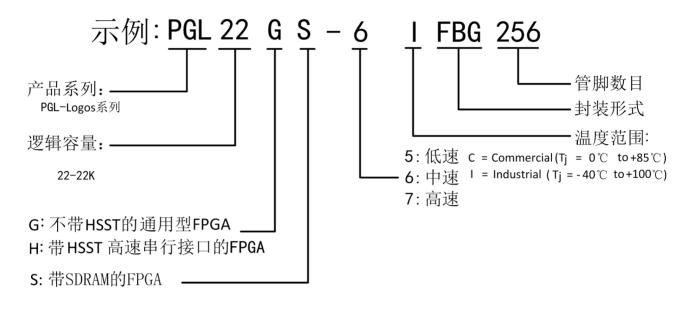

Logos系列FPGA产品型号的编号内容及意义如图1所示。

图 1 Logos系列FPGA产品型号的编号内容及意义

产品质量等级说明如下表 6所示。

表 6 产品质量等级说明

|       |         | 速度等级和温度范围      |                |  |  |

|-------|---------|----------------|----------------|--|--|

| 产品系列  | 器件      | Commercial (C) | Industrial (I) |  |  |

|       |         | 0°C to 85°C    | -40℃ to 100℃   |  |  |

|       | PGL12G  | -6C            | -6I            |  |  |

|       | PGL22G  | -6C            | -6I            |  |  |

| Logog | PGL25G  | -6C            | -6I            |  |  |

| Logos | PGL50G  | -6C            | -6I            |  |  |

|       | PGL50H  | -6C            | -6I            |  |  |

|       | PGL100H | -6C            | -61            |  |  |

DS02001 (v2.6) 第 **18 / 48**页

## 2 工作条件

#### 2.1 器件绝对极限电压

表 7 器件最大绝对电压值

| 次 · 開刊   |                             |       |      |    |  |  |  |  |  |

|----------|-----------------------------|-------|------|----|--|--|--|--|--|

| 名称       | 描述                          | 最小值   | 最大值  | 单位 |  |  |  |  |  |

| VCC      | 内核电源电压                      | -0.16 | 1.32 | V  |  |  |  |  |  |

| VCCAUX   | 辅助电源电压(给IOB、LDO等供电)         | -0.16 | 3.63 | V  |  |  |  |  |  |

| VCCAUX_A | 辅助电源电压(给ADC、POR、Bandgap等供电) | -0.16 | 3.63 | V  |  |  |  |  |  |

| VCCIO    | BANK IO电源电压                 | -0.16 | 3.63 | V  |  |  |  |  |  |

| VCCEFUSE | Efuse编程电压                   | -0.16 | 3.63 | V  |  |  |  |  |  |

| VCCIOCFG | BANKCFG电源电压                 | -0.16 | 3.63 | V  |  |  |  |  |  |

| $V_{I}$  | 直流输入电压                      | -0.16 | 3.63 | V  |  |  |  |  |  |

注:超过上述极限额定值可能导致器件永久性损坏。在额定值下操作不会损坏器件,但不表示器件在此极限值下功能正常。器件长期在极限条件下工作,会严重影响器件的可靠性。

## 2.2 输入AC过冲极限值

表 8 10输入AC过冲电压极限值

| 输入PIN       | 过冲电压       | 一 夜 o 10 棚 /    | 温度       | 条件   | 极限值   | 单位 |

|-------------|------------|-----------------|----------|------|-------|----|

| 1000 41 111 | ZII BE     | 79 <b>6</b> 1 H | <u> </u> | DC   | 4.02  | V  |

|             |            |                 |          | 55%  | 4.07  | V  |

|             |            |                 |          | 30%  | 4.12  | V  |

|             |            |                 |          | 17%  | 4.17  | V  |

|             |            |                 |          | 9.5% | 4.22  | V  |

|             |            |                 |          | 5.5% | 4.27  | V  |

|             | OVERSHOOT  | 工业              | 100℃     | 3.1% | 4.32  | V  |

|             |            |                 |          | 1.7% | 4.37  | V  |

|             |            |                 |          | 1.0% | 4.42  | V  |

|             |            |                 |          | 0.5% | 4.47  | V  |

|             |            |                 |          | 0.3% | 4.52  | V  |

|             |            |                 |          | 0.2% | 4.57  | V  |

| I/O输入电压,    |            |                 |          | 0.1% | 4.62  | V  |

| 相对于地        |            |                 |          | DC   | -0.16 | V  |

|             |            |                 |          | 72%  | -0.21 | V  |

|             |            |                 |          | 55%  | -0.26 | V  |

|             |            |                 |          | 40%  | -0.31 | V  |

|             |            |                 |          | 30%  | -0.36 | V  |

|             |            |                 |          | 22%  | -0.41 | V  |

|             | UNDERSHOOT | 工业              | 100℃     | 17%  | -0.46 | V  |

|             |            |                 |          | 12%  | -0.51 | V  |

|             |            |                 |          | 10%  | -0.56 | V  |

|             |            |                 |          | 8%   | -0.61 | V  |

|             |            |                 |          | 6%   | -0.66 | V  |

|             |            |                 |          | 4%   | -0.71 | V  |

|             |            |                 |          | 3%   | -0.76 | V  |

DS02001 (v2.6) 第 **19 / 48**页

#### 2.3 器件推荐工作条件

表 9 PGL12G、PGL22G推荐工作条件

| 名称                        | 描述               | 最小值   | 典型值 | 最大值   | 单位                     |

|---------------------------|------------------|-------|-----|-------|------------------------|

| VCC                       | 内核电源电压           | 1.045 | 1.1 | 1.155 | V                      |

| VCCAUX                    | 辅助电源电压(给IOB、LDO等 | 3.135 | 3.3 | 3.465 | V                      |

|                           | 供电)              |       |     |       |                        |

| VCCAUX_A 辅助电源电压(给ADC、POR、 |                  | 3.135 | 3.3 | 3.465 | V                      |

|                           | Bandgap等供电)      |       |     |       |                        |

| VCCIO                     | BANK IO电源电压      | 1.14  |     | 3.465 | V                      |

| VCCEFUSE                  | Efuse编程电压        | 3.135 | 3.3 | 3.465 | V                      |

| VCCIOCFG                  | BANKCFG电源电压      | 1.425 |     | 3.465 | V                      |

| T <sub>J</sub> (商业级)      | 商业级芯片工作温度        | 0     |     | 85    | $^{\circ}\!\mathbb{C}$ |

| T <sub>J</sub> (工业级)      | 工业级芯片工作温度        | -40   |     | 100   | $^{\circ}\mathbb{C}$   |

注: 推荐工作电压在典型工作电压偏离±5%范围内。

表 10 PGL25G推荐工作条件

|                      | X 10 1 11 21 3(1)       |       |     |       |              |  |  |  |  |  |  |

|----------------------|-------------------------|-------|-----|-------|--------------|--|--|--|--|--|--|

| 名称                   | 描述                      | 最小值   | 典型值 | 最大值   | 单位           |  |  |  |  |  |  |

| VCC                  | 内核电源电压                  | 1.14  | 1.2 | 1.26  | V            |  |  |  |  |  |  |

| VCCAUX               | 辅助电源电压,包含BANK配置电压、Efuse | 3.135 | 3.3 | 3.465 | V            |  |  |  |  |  |  |

|                      | 编程电压等                   |       |     |       |              |  |  |  |  |  |  |

| VCCIO                | BANK IO电源电压             | 1.14  |     | 3.465 | V            |  |  |  |  |  |  |

| T <sub>J</sub> (商业级) | 商业级芯片工作温度               | 0     |     | 85    | $^{\circ}$ C |  |  |  |  |  |  |

| T」(工业级)              | 工业级芯片工作温度               | -40   |     | 100   | $^{\circ}$   |  |  |  |  |  |  |

注: 推荐工作电压在典型工作电压偏离±5%范围内。

表 11 PGL50G、PGL50H、PGL100H推荐工作条件

| 名称                   | 描述          |             | 最小值   | 典型值  | 最大值   | 单位                   |

|----------------------|-------------|-------------|-------|------|-------|----------------------|

| VCC                  | 内核电源电压      | 1.14        | 1.2   | 1.26 | V     |                      |

| VCCATIV              | 辅助电源电压,     | VCCAUX=3.3V | 3.135 | 3.3  | 3.465 | V                    |

| VCCAUX               | 包含BANK配置电压等 | VCCAUX=2.5V | 2.375 | 2.5  | 2.625 | V                    |

| VCCIO                | BANK IO电源电压 |             | 1.14  |      | 3.465 | V                    |

| VCCEFUSE             | Efuse编程电压   |             | 3.135 | 3.3  | 3.465 | V                    |

| T <sub>J</sub> (商业级) | 商业级芯片工作温度   |             | 0     |      | 85    | $^{\circ}\mathbb{C}$ |

| T <sub>J</sub> (工业级) | 工业级芯片工作温度   |             | -40   |      | 100   | $^{\circ}\mathbb{C}$ |

注: 推荐工作电压在典型工作电压偏离±5%范围内。

## 2.4 ESD (HBM, CDM), Latch Up指标

表 12 ESD、Latch-Up指标

| Human Body Model (HBM) | Charge Device Model (CDM) | Latch-up |  |  |

|------------------------|---------------------------|----------|--|--|

| ±2000V                 | ±500V                     | ±100mA   |  |  |

DS02001 (v2.6) 第 **20 / 48**页

## 3 直流特性

## 3.1 Hot-Socketing直流特性

表 13 热插拔直流特性

|          | <b>以 16 </b> |                                                                                                                                                            |     |     |        |        |  |  |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------|--------|--|--|

| 参数符号     | 参数描述         | 条件(clamp功能关闭)                                                                                                                                              | 最小值 | 典型值 | 最大值    | 注释     |  |  |

| $I_{DK}$ | 最大泄漏电流       | $ \begin{array}{l} -0.5V < V_{IN} < VCCIO_{MAX} \\ 0V < VCC < VCC \; (max), \\ 0V < VCCIO < VCCIO \; (max), \\ 0V < VCCAUX < VCCAUX \\ (max) \end{array} $ | -   | -   | +/-1mA | 每一个pad |  |  |

注1: Vtp 为PMOS的阈值电压绝对值

DS02001 (v2.6) 第 **21 / 48**页

## 3.2 IO输入输出直流特性

各单端IO电平标准输入输出电压范围如下表 14。

表 14 单端10电平标准输入输出电压范围

| 单端IO                       | VI   | L(V)        | VIH         | (V)   | VOL (V) | VOH(V)     |

|----------------------------|------|-------------|-------------|-------|---------|------------|

| 平圳IU                       | 最小值  | 最大值         | 最小值         | 最大值   | 最大值     | 最小值        |

| LVTLL33<br>LVCMOS33        | -0.3 | 0.8         | 2           | 3.465 | 0.4     | VCCIO-0.4  |

| LVCMOS25                   | -0.3 | 0.7         | 1.7         | 3.465 | 0.4     | VCCIO-0.4  |

| LVCMOS18                   | -0.3 | 0.35VCCIO   | 0.65VCCIO   | 3.465 | 0.4     | VCCIO-0.4  |

| LVCMOS15                   | -0.3 | 0.35VCCIO   | 0.65VCCIO   | 3.465 | 0.4     | VCCIO_0.4  |

| LVCMOS12                   | -0.3 | 0.35VCCIO   | 0.65VCCIO   | 3.465 | 0.4     | VCCIO-0.4  |

| SSTL25_I                   | -0.3 | VREF -0.18  | VREF +0.18  | 3.465 | 0.54    | VCCIO-0.62 |

| SSTL25_II                  | -0.3 | VREF -0.18  | VREF +0.18  | 3.465 | 0.35    | VCCIO-0.43 |

| SSTL18_I                   | -0.3 | VREF -0.125 | VREF +0.125 | 3.465 | 0. 4    | VCCIO-0.4  |

| SSTL18_II                  | -0.3 | VREF -0.125 | VREF +0.125 | 3.465 | 0.28    | VCCIO-0.28 |

| SSTL15_I<br>SSTL15_I_DCI   | -0.3 | VREF-0.1    | VREF+0.1    | 3.465 | 0.31    | VCCIO-0.31 |

| SSTL15_II<br>SSTL15_II_DCI | -0.3 | VREF-0.1    | VREF+0.1    | 3.465 | 0.31    | VCCIO-0.31 |

| HSTL18_I                   | -0.3 | VREF-0.1    | VREF+0.1    | 3.465 | 0. 4    | VCCIO-0.4  |

| HSTL18_II                  | -0.3 | VREF-0.1    | VREF+0.1    | 3.465 | 0. 4    | VCCIO-0.4  |

| HSTL15_I<br>HSTL15_I_DCI   | -0.3 | VREF-0.1    | VREF+0.1    | 3.465 | 0. 4    | VCCIO-0.4  |

注: 仅PGL22G支持DCI

DS02001 (v2.6) 第 **22 / 48**页

各单端IO电平标准输出电流见下表。

表 15 单端10电平标准输出电流

| 单端IO          | IOL(mA) | IOH(mA) | VREF(V)                  | VTT(V)     |

|---------------|---------|---------|--------------------------|------------|

|               | 4       | -4      | -                        | -          |

|               | 8       | -8      | _                        | _          |

| LVTTL         | 12      | -12     | _                        | _          |

| LVCMOS33      | 16      | -16     | _                        | _          |

|               | 24      | -24     | _                        | _          |

|               | 4       | -4      | _                        | _          |

|               | 8       | -8      | _                        | _          |

| LVCMOS25      | 12      | -12     | _                        | _          |

|               | 16      | -16     | _                        | _          |

|               | 4       | -4      | _                        | _          |

| LVCMOS18      | 8       | -8      | _                        | _          |

|               | 12      | -12     | _                        | _          |

|               | 4       | -4      | _                        | -          |

| LVCMOS15      | 8       | -8      | _                        | _          |

|               | 2       | -2      | -                        | -          |

| LVCMOS12      | 6       | -6      | _                        | -          |

| COTT AT I     | -       | -       | 0.45VCCIO                |            |

| SSTL25_I      | 8.1     | -8.1    | 0.5VCCIO                 |            |

|               |         |         | 0.55VCCIO                | 0.5VCCIO   |

| COTT OF II    |         |         | 0.45VCCIO                |            |

| SSTL25_II     | 16.2    | -16.2   | 0.5VCCIO                 |            |

|               |         |         | 0.55VCCIO                | 0.5VCCIO   |

| SSTL18 I      |         |         | 0.45VCCIO                |            |

| 551L10_1      | 6.7     | -6.7    | 0.5VCCIO                 |            |

|               |         |         | 0.55VCCIO                | 0.5VCCIO   |

| SSTL18 II     |         |         | 0.45VCCIO                |            |

| 551110_11     | 13.4    | -13.4   | 0.5VCCIO                 |            |

|               |         |         | 0.55VCCIO                | 0.5VCCIO   |

| SSTL15_I      |         |         | 0.45VCCIO                |            |

| SSTL15 I DCI  | 7.5     | -7.5    | 0.5VCCIO                 |            |

| SSTEIC_I_BCI  |         |         | 0.55VCCIO                | 0.5VCCIO   |

| SSTL15 II     |         |         | 0.45VCCIO                |            |

| SSTL15 II DCI | 8.8     | -8.8    | 0.5VCCIO                 | 0.5110010  |

|               |         |         | 0.55VCCIO                | 0.5VCCIO   |

| HSTL18_I      |         | 0       | 0.45VCCIO                |            |

| _             | 8       | -8      | 0.5VCCIO                 | 0.51/0010  |

|               |         |         | 0.55VCCIO                | 0.5VCCIO   |

| HSTL18_II     | 16      | -16     | 0.45VCCIO<br>0.5VCCIO    |            |

|               | 10      | -10     | 0.55VCCIO<br>0.55VCCIO   | 0.5VCCIO   |

|               |         |         | 0.33 VCCIO<br>0.45 VCCIO | 0.5 V CC10 |

| HSTL15_I      | 8       | -8      | 0.43 VCCIO<br>0.5 VCCIO  |            |

| HSTL15_I_DCI  | o       | -0      | 0.55VCCIO<br>0.55VCCIO   | 0.5VCCIO   |

|               | 1       |         | 1 0.33 V CCIO            | 0.5 V CC10 |

注: 仅PGL22G支持DCI, PGL22GS\_LPG176 L0 BANK不支持用到VREF的所有电平标准。

DS02001 (v2.6) 第 **23 / 48**页

表 16 输入10电平标准的BANK支持说明

|   |    | IO标准                                                                                                                               |                              |                              |                   | 器件                | :               |                 |                 |                                  |

|---|----|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------|-------------------|-----------------|-----------------|-----------------|----------------------------------|

|   | 模  |                                                                                                                                    | PGL                          | 22G                          | PGI               | PGL12G            |                 | /PGL50G<br>L50H | PGL<br>100H     |                                  |

| 输 | 式  |                                                                                                                                    | BANKL0,<br>BANKL1,<br>BANKL2 | BANKR0,<br>BANKR1,<br>BANKR2 | BANKL0,<br>BANKL1 | BANKR0,<br>BANKR1 | BANK0,<br>BANK2 | BANK1,<br>BANK3 | BANK0,<br>BANK2 | BANK1<br>BANK3<br>BANK4<br>BANK5 |

|   | 单端 | LVCMOS12<br>LVCMOS15<br>LVCMOS18<br>LVCMOS25<br>LVCMOS33<br>SSTL15_I<br>SSTL15_II<br>SSLT18_I<br>SSTL18_II<br>SSTL25_I<br>SSTL25_I | 支持                           | 支持                           | 支持                | 支持                | 支持              | 支持              | 支持              | 支持                               |

| 入 |    | SSTL15_I_DCI<br>SSTL15_II_DCI<br>HSTL15_I_DCI                                                                                      | 支持                           | 支持                           | 不支持               | 不支持               | 不支持             | 不支持             | 不支持             | 不支持                              |

|   | 差分 | LVPECL33 LVDS25 SLVS MINI-LVDS SUB-LVDS TMDS RSDS PPDS TMDS SSTL15D_I SSTL15D_I HSTL15D_I MIPI                                     | 支持                           | 支持                           | 支持                | 支持                | 支持              | 支持              | 支持              | 支持                               |

|   |    | SSTL15D_I_DCI<br>SSTL15D_II_DCI<br>HSTL15D_I_DCI                                                                                   | 支持                           | 支持                           | 不支持               | 不支持               | 不支持             | 不支持             | 不支持             | 不支持                              |

表 17 输出IO电平标准的BANK支持说明

|    |    | IO标准                                                                                                                      | 1                            | 器件                           |                   |                   |                 |                 |                 |                                  |  |

|----|----|---------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------|-------------------|-----------------|-----------------|-----------------|----------------------------------|--|

|    | 模  |                                                                                                                           | PGI                          | L22G                         | PGL               | PGL12G PGL        |                 | PGL25G/PGL50G/  |                 | L                                |  |

|    |    |                                                                                                                           |                              |                              |                   |                   | PGL             | .50H            | 100Н            |                                  |  |

|    | 式  |                                                                                                                           | BANKL0,<br>BANKL1,<br>BANKL2 | BANKR0,<br>BANKR1,<br>BANKR2 | BANKL0,<br>BANKL1 | BANKR0,<br>BANKR1 | BANK0,<br>BANK2 | BANK1,<br>BANK3 | BANK0,<br>BANK2 | BANK1<br>BANK3<br>BANK4<br>BANK5 |  |

| 输出 | 单端 | LVCMOS12<br>LVCMOS15<br>LVCMOS18<br>LVCMOS25<br>LVCMOS33<br>SSTL15_II<br>SSTL15_II<br>SSTL18_II<br>SSTL18_II<br>SSTL25_II | 支持                           | 支持                           | 支持                | 支持                | 支持              | 支持              | 支持              | 支持                               |  |

DS02001 (v2.6) 第 **24 / 48**页

|       | SSTL15_I_DCI<br>SSTL15_II_DCI<br>HSTL15_I_DCI   | 支持 | 支持 | 不支持 | 不支持 | 不支持 | 不支持 | 不支持 | 不支持 |

|-------|-------------------------------------------------|----|----|-----|-----|-----|-----|-----|-----|

| 差分    | LVDS25<br>SLVS<br>MINI-LVDS<br>SUB-LVDS<br>TMDS | 支持 | 支持 | 不支持 | 支持  | 支持  | 不支持 | 支持  | 不支持 |

| 类 差 分 | PPDS<br>RSDS<br>LVPECL33                        | 支持 | 支持 | 支持  | 支持  | 支持  | 支持  | 支持  | 支持  |

表 18 双向10电平标准的BANK支持说明

|     | 表 18 双回10电半标准的BANK支持说明 |                                                                                                                                    |                              |                              |                   |                   |                 |                 |                 |                                  |

|-----|------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------|-------------------|-----------------|-----------------|-----------------|----------------------------------|

|     |                        |                                                                                                                                    |                              |                              |                   | 器件                |                 |                 |                 |                                  |

|     | +#                     |                                                                                                                                    | PGI                          | .22G                         | PGI               | L12G              | PGL25G/         | PGL50G/         | PC              | GL                               |

|     | 模                      | IO标准                                                                                                                               |                              |                              |                   |                   | PGL             | 50H             | 100H            |                                  |

|     | 式                      |                                                                                                                                    | BANKL0,<br>BANKL1,<br>BANKL2 | BANKR0,<br>BANKR1,<br>BANKR2 | BANKL0,<br>BANKL1 | BANKR0,<br>BANKR1 | BANK0,<br>BANK2 | BANK1,<br>BANK3 | BANK0,<br>BANK2 | BANK1<br>BANK3<br>BANK4<br>BANK5 |

|     | 单端                     | LVCMOS12<br>LVCMOS15<br>LVCMOS18<br>LVCMOS25<br>LVCMOS33<br>SSTL15_I<br>SSTL15_II<br>SSTL18_I<br>SSTL18_II<br>SSTL25_I<br>SSTL25_I | 支持                           | 支持                           | 支持                | 支持                | 支持              | 支持              | 支持              | 支持                               |

| 双向  |                        | SSTL15_I_DCI<br>SSTL15_II_DCI<br>HSTL15_I_DCI                                                                                      | 支持                           | 支持                           | 不支持               | 不支持               | 不支持             | 不支持             | 不支持             | 不支持                              |

| III | 差分                     | LVDS25<br>MINI-LVDS<br>SUB-LVDS<br>SLVS<br>TMDS                                                                                    | 不支持                          | 不支持                          | 不支持               | 不支持               | 不支持             | 不支持             | 不支持             | 不支持                              |

|     | 类                      | SSTL15D_I<br>SSTL15D_II<br>HSTL15D_I<br>SSTL18D_I                                                                                  | 去柱                           | 士柱                           | 支持                | 支持                | 支持              | 子柱              | 子柱              | 支持                               |

|     | 差                      | SSTL25D_I<br>SSTL25D_II                                                                                                            | 支持                           | 支持                           | 又                 | 又行                | 又行              | 支持              | 支持              | 又行<br>                           |

|     | 分                      | LVPECL33                                                                                                                           |                              |                              |                   |                   |                 |                 |                 |                                  |

|     | 75                     | PPDS                                                                                                                               |                              |                              |                   |                   |                 |                 |                 |                                  |

|     |                        | RSDS                                                                                                                               |                              |                              |                   |                   |                 |                 |                 |                                  |

|     |                        | SSTL15D_I_DCI<br>SSTL15D_II_DCI<br>HSTL15D_I_DCI                                                                                   | 支持                           | 支持                           | 不支持               | 不支持               | 不支持             | 不支持             | 不支持             | 不支持                              |

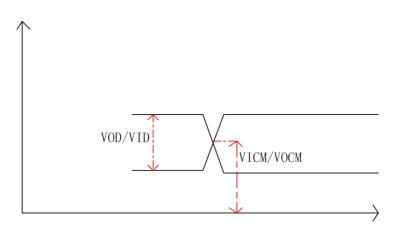

差分IO电平标准的主要电气特性参数定义如下图,输入输出电压范围如表 19和表 20所示。

DS02001 (v2.6) 第 **25 / 48**页

0.46

1.1

差分电气特性参数

VICM VID 标准 输入共模电平 (V) 输入差模电平 (V) min typ max min typ max LVDS25 0.5 1.2 1.9 0.1 0.35 0.5 **MINI-LVDS** 1.9 0.2 0.4 0.4 0.6 **SUB-LVDS** 0.6 0.9 1.2 0.08 0.1 0.2

表 19 差分输入标准的参数要求

| = | 20 | 差分输出标准的参数要求 |

|---|----|-------------|

| ᅏ | 70 | 麦分蜊出标准的参数发来 |

0.3

1.9

0.08

0.3

|           |      | VOCM     |      |      | VOD       |      |

|-----------|------|----------|------|------|-----------|------|

| 标准        | 输    | 〕出共模电平 ( | V)   | 车    | 输出差模电平(V) |      |

|           | min  | typ      | max  | min  | typ       | max  |

| LVDS25    | 1    | 1.25     | 1.4  | 0.25 | 0.35      | 0.45 |

| MINI-LVDS | 1    | 1.2      | 1.4  | 0.3  |           | 0.6  |

| SUB-      | 0.8  | 0.9      | 1    | 0.1  | 0.15      | 0.2  |

| LVDS      | 0.8  | 0.9      | 1    | 0.1  | 0.13      | 0.2  |

| SLVS      | 0.15 | 0.2      | 0.25 | 0.14 | 0.2       | 0.27 |

## 4 交流特性

SLVS

LVPECL33

本章主要列出了Logos系列FPGA各逻辑单元在典型工作条件下的交流特性。

0.07

0.5

### 4.1 IO交流特性参数

IOB的开关特性如表 21所示。

表 21 IOB的输入输出延时

| I/O标准             | T <sub>IOPI</sub> | T <sub>IOOP</sub> | T <sub>IOTP</sub> | 单位 |

|-------------------|-------------------|-------------------|-------------------|----|

| 1/04和臣            | -6                | -6                | -6                |    |

| LVTTL, 4mA, Slow  | 1.50              | 2.86              | 2.86              | ns |

| LVTTL, 8mA, Slow  | 1.50              | 2.76              | 2.76              | ns |

| LVTTL, 12mA, Slow | 1.50              | 2.66              | 2.66              | ns |

| LVTTL, 16mA, Slow | 1.50              | 2.56              | 2.56              | ns |

| LVTTL, 24mA, Slow | 1.50              | 2.46              | 2.46              | ns |

| LVTTL, 4mA, Fast  | 1.50              | 2.80              | 2.80              | ns |

DS02001 (v2.6) 第 **26 / 48**页

|                      |      | I    |      | 1  |

|----------------------|------|------|------|----|

| LVTTL, 8mA, Fast     | 1.50 | 2.70 | 2.70 | ns |

| LVTTL, 12mA, Fast    | 1.50 | 2.60 | 2.60 | ns |

| LVTTL, 16mA, Fast    | 1.50 | 2.50 | 2.50 | ns |

| LVTTL, 24mA, Fast    | 1.50 | 2.40 | 2.40 | ns |

| LVCMOS33, 4mA, Slow  | 1.50 | 2.86 | 2.86 | ns |

| LVCMOS33, 8mA, Slow  | 1.50 | 2.76 | 2.76 | ns |

| LVCMOS33, 12mA, Slow | 1.50 | 2.66 | 2.66 | ns |

| LVCMOS33, 16mA, Slow | 1.50 | 2.56 | 2.56 | ns |

| LVCMOS33, 24mA, Slow | 1.50 | 2.46 | 2.46 | ns |

| LVCMOS33, 4mA, Fast  | 1.50 | 2.80 | 2.80 | ns |

| LVCMOS33, 8mA, Fast  | 1.50 | 2.70 | 2.70 | ns |

| LVCMOS33, 12mA, Fast | 1.50 | 2.60 | 2.60 | ns |

| LVCMOS33, 16mA, Fast | 1.50 | 2.50 | 2.50 | ns |

| LVCMOS33, 24mA, Fast | 1.50 | 2.40 | 2.40 | ns |

| LVCMOS25, 4mA, Slow  | 1.80 | 2.96 | 2.96 | ns |

| LVCMOS25, 8mA, Slow  | 1.80 | 2.86 | 2.86 | ns |

| LVCMOS25, 12mA, Slow | 1.80 | 2.76 | 2.76 | ns |

| LVCMOS25, 16mA, Slow | 1.80 | 2.66 | 2.66 | ns |

| LVCMOS25, 4mA, Fast  | 1.80 | 2.90 | 2.90 | ns |

| LVCMOS25, 8mA, Fast  | 1.80 | 2.80 | 2.80 | ns |

| LVCMOS25, 12mA, Fast | 1.80 | 2.70 | 2.70 | ns |

| LVCMOS25, 16mA, Fast | 1.80 | 2.60 | 2.60 | ns |

| LVCMOS18, 4mA, Slow  | 2.90 | 3.26 | 3.26 | ns |

| LVCMOS18, 8mA, Slow  | 2.90 | 3.06 | 3.06 | ns |

| LVCMOS18, 12mA, Slow | 2.90 | 2.86 | 2.86 | ns |

| LVCMOS18, 4mA, Fast  | 2.90 | 3.20 | 3.20 | ns |

| LVCMOS18, 8mA, Fast  | 2.90 | 3.00 | 3.00 | ns |

| LVCMOS18, 12mA, Fast | 2.90 | 2.80 | 2.80 | ns |

| LVCMOS15, 4mA, Slow  | 3.60 | 3.36 | 3.36 | ns |

| LVCMOS15, 8mA, Slow  | 3.60 | 3.16 | 3.16 | ns |

| LVCMOS15, 4mA, Fast  | 3.60 | 3.30 | 3.30 | ns |

| LVCMOS15, 8mA, Fast  | 3.60 | 3.10 | 3.10 | ns |

|                      |      |      |      |    |

#### 续表 20 IOB的输入输出延时

| I/O标准               |      | T <sub>IOOP</sub> | T <sub>IOTP</sub> | 单位 |

|---------------------|------|-------------------|-------------------|----|

|                     |      | -6                | -6                |    |

| LVCMOS12, 2mA, Slow | 6.40 | 4.46              | 4.46              | ns |

| LVCMOS12, 6mA, Slow | 6.40 | 3.66              | 3.66              | ns |

| LVCMOS12, 2mA, Fast | 6.40 | 4.40              | 4.40              | ns |

| LVCMOS12, 6mA, Fast | 6.40 | 3.60              | 3.60              | ns |

| SSTL25_I            | 1.20 | 2.80              | 2.80              | ns |

| SSTL25_II           | 1.20 | 2.80              | 2.80              | ns |

| SSTL18_I            | 1.30 | 3.00              | 3.00              | ns |

| SSTL18_II           | 1.30 | 3.00              | 3.00              | ns |

| SSTL15_I            | 1.60 | 3.00              | 3.00              | ns |

| SSTL15_II           | 1.60 | 3.00              | 3.00              | ns |

| SSTL135             | 1.80 | 3.30              | 3.30              | ns |

| HSTL18_I            | 1.30 | 3.00              | 3.00              | ns |

| HSTL18_II           | 1.30 | 3.00              | 3.00              | ns |

| HSTL15_I            | 1.60 | 3.00              | 3.00              | ns |

| LVDS25              | 1.20 | 2.40              | 2.40              | ns |

| MINI_LVDS           | 1.20 | 2.40              | 2.40              | ns |

DS02001 (v2.6) 第 **27 / 48**页

| SUB_LVDS   | 1.20 | 2.40 | 2.40 | ns |

|------------|------|------|------|----|

| SLVS       | 1.20 | 2.40 | 2.40 | ns |

| TMDS       | 1.20 | 2.40 | 2.40 | ns |

| PPDS       | 1.20 | 2.40 | 2.40 | ns |

| LVPECL     | 1.20 | 2.40 | 2.40 | ns |

| RSDS       | 1.20 | 2.40 | 2.40 | ns |

| BLVDS      | 1.20 | 2.40 | 2.40 | ns |

| SSTL25D_I  | 1.20 | 2.80 | 2.80 | ns |

| SSTL25D_II | 1.20 | 2.80 | 2.80 | ns |

| SSTL18D_I  | 1.30 | 3.00 | 3.00 | ns |

| SSTL18D_II | 1.30 | 3.00 | 3.00 | ns |

| SSTL15D_I  | 1.60 | 3.00 | 3.00 | ns |

| SSTL15D_II | 1.60 | 3.00 | 3.00 | ns |

| SSTL135D   | 2.00 | 3.30 | 3.30 | ns |

| HSTL18D_I  | 1.30 | 3.00 | 3.00 | ns |

| HSTL18D_II | 1.30 | 3.00 | 3.00 | ns |

| HSTL15D_I  | 1.60 | 3.00 | 3.00 | ns |

T<sub>IOPI</sub>: 从IOB Pad经过IBUF到达IOBUFFER的DIN的延时。 T<sub>IOOP</sub>: 从IOBUFFER的DO经过OBUF到达IOB Pad的延时。 T<sub>IOTP</sub>: 从IOBUFFER的TO经过OBUF到达IOB Pad的延时。

表 22 IOB三态使能时的输出开关特性

|            |                               | 速度等级 | 单位 |

|------------|-------------------------------|------|----|

| <b>光</b> 別 | <b>付任参数抽处</b>                 | -6   |    |

| Тютрнх     | T input to Pad high-impedance | 2.7  | ns |

注: TIOTPHZ参数为三态使能时,从IOBUFFER的TO经过OBUF到达IOB Pad的延时。

DS02001 (v2.6) 第 **28 / 48**页

IOL的交流特性如表 23至表 25所示。

表 23 IOL寄存器交流参数

| 米別                                                                                                                                                                                                                                                                                                               | 交流特性参数描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 数值            | 单位 | 备注     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|----|--------|--|--|--|

| 大加                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | -6            | 平位 | 無任     |  |  |  |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _      |               |    |        |  |  |  |

|                                                                                                                                                                                                                                                                                                                  | CE -> CLK setup/hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 上升沿    | 0.131/-0.044  | ns |        |  |  |  |

|                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 下降沿    | 0.064/-0.031  | ns |        |  |  |  |

|                                                                                                                                                                                                                                                                                                                  | LRS -> CLK setup/hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 上升沿    | 0.277/-0.099  | ns |        |  |  |  |